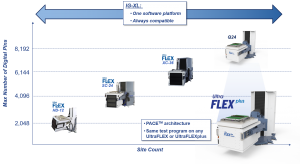

On September 4, 2019, Teradyne (NASDAQ: TER), the world's leading provider of automated test solutions, launched UltraFLEXplus, the newest member of the UltraFLEX tester family in North Kenting, Massachusetts, USA, the first application of the PACE architecture. . UltraFLEXplus addresses the emerging digital testing needs of today's artificial intelligence and 5G communications infrastructure.

The increase in test characterization requirements and volume production data has gradually challenged the limits of the current test machine architecture, resulting in an extension of the development cycle and an increase in mass production test time. In response to this emerging challenge, Teradyne developed the PACE multi-controller architecture for UltraFLEXplus. This revolutionary technology enables test engineers to more efficiently debug and characterize complex chips, enabling less work and higher tester utilization, bringing new products to market faster.

UltraFLEXplus combines a breakthrough PACE architecture with industry-leading IG-XL software to ensure that semiconductor companies can successfully address these new test challenges. Teradyne's IG-XL software not only provides customers with a comprehensive development environment, but also utilizes the installed capacity of more than 4,000 UltraFLEX testers. This enabled 10,000 IG-XL-trained test engineers to develop flexible test procedures.

"It is expected that the test data of the SOC chip will be eight times that of 2018 in 2025. Whether it is the amount of data required to fully test the chip, or the number of test results that must be retained after the test yield and performance analysis." Greg Smith, president of Teradyne's Semiconductor Tests Division, said, "In order to bring these chips to market and provide an industry-leading test economy, we believe that fundamental improvements in the ATE architecture system are a must."